|

#1

| |||

| |||

|

I want to get some information about the Vector Institute at Hyderabad. So will you provide me information about the Vector Institute and also provide me course content of VLSI Training Course at Vector Institute?

|

|

#2

| ||||

| ||||

|

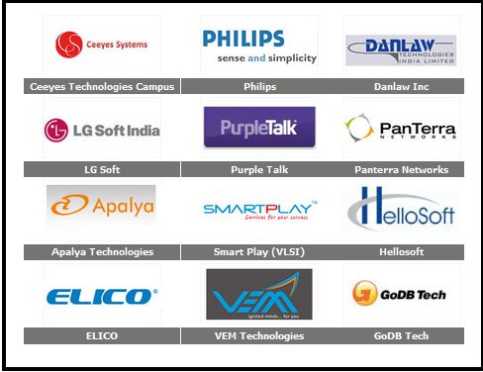

The Vector Institute is an ISO 9001:2008 Certified Institute. Training Courses Embedded Systems VLSI Short Term Courses Programming C Programming C++ Programming C/C++ with Data structures Objective C Microcontroller 8051 Microcontroller ARM AVR Pic Device Drivers Device Drivers For ARM9 Device Drivers For PC Operting Sys / RTOS Linux Internals Embedded Linux VxWorks RT Linux RTX51 Moblie Applications Iphone Android Windows Mobile Blackberry Course Content VLSI ASIC / FPGA DESIGN ASIC / FPGA Design Fundamentals Advanced Digital Design CMOS MOS Fundamentals and Characterization Different Styles of Fabrication for NMOS/PMOS/CMOS Design with CMOS Gates Scaling Effects Subsystem Design Design Exercise using CMOS Different Methodologies for IC Design Fabrication Flows and Fundamentals NMOS/PMOS/CMOS Technologies Fabrication Principles Sub-Micron Designs Characterization of CMOS Circuits Layout Representation for CMOS Circuits Introduction of IC Design Parasitic Extraction and Calculations VHDL VHDL Overview and Concepts Levels of Abstraction Data Types and declaration Relational, Logical, Arithmetic Operators Process Statement Concurrent Statements If-then-else, Case Delta Delay Concept Arrays, Memory Modeling, FSM Behavioral / RTL Coding Structural Coding Generate Statement Local and Global Declarations Assertion based verification Generics and Generic maps Entity, Architecture Sequential Statement Signal and Variables, Constants Slicing and Concatenation Loop Statements When-else, With-select Enumerated Data Types Writing Functions Configuration Block Libraries, Standard packages Component declarations and installations Writing Procedures Operator Overloading Files read and write operations Package, Package body Writing Test Benches Code for complex FPGA and ASICs VERILOG Language introduction Module, Ports types and declarations Identifiers, Parameters Writing expressions Continuous Assignments Procedural Statements Operation Control Statements If, case Combination and sequential circuit designs Memory modeling,, state machines Writing Tasks Conditional Compilation System Tasks User defined primitives Assertion based verification Advanced topics Levels of abstraction Behavioral Modeling Structural Coding Relational, Arithmetic, Logical, Bit-wise shift Operators Always, Initial Blocks, begin ebd, fork join Blocking and Non-blocking statements Registers and nets, Arrays Loops: while, for-loop, for-each, repeat Writing Functions Compiler directives CMOS gate modeling Delays, Specify block Testbenchs, modeling, timing checks Gate level primitives Code for synthesis Writing reusable code System Verilog Introduction to System Verilog System Verilog Procedural Blocks, Tasks and Function Modelling Finite State Machines with System Verilog System Verilog Design Hierarchy Behavioral and Transaction Level Modelling System Verilog Declaration spaces System Verilog Procedural Statements System Verilog Arrays, Structures and Unions System Verilog Interfaces System Verilog Literal Values and Built-in Data Types System Verilog User-Defined and Enumerated Types FPGA Flow Architectures of XILINX, ALTERA Devices Designing with FPGAs Architecture based coding Efficient resource utilization False paths and multi cycle paths Back annotation, Gate level simulation, SDF Format DSP on FPGA Hands on experience with industry Standard Tools FPGA’s and its Design Flows Timing analysis/Floor Planning Place and route/RPM Constrains based synthesis Re-configurable Devices, FPGA’s/CPLD’s Writing Scripts UCF file creation ASIC Flow Projects: As a part of course 2 mini projects and 1 major project False paths / Multi cycle paths / Critical paths Scan Insertion / Types of Scan Logic BIST, Memory BIST, ATGP, Boundary Scan Layout Design Diagnosis, DFM, Yield Analysis SOC Design and Trade-offs ASIC Case Studies Clock Tree Synthesis Fault Models EDA Tools / CAD Flow for IC Design Simulation/Synthesis using ASIC libraries Design for Testability (DFT) LVS/DRC/OPC/Physical verification Scan Diagnostics Future Trends and challenges Placing and Routing Pattern Compression Facilities Systems Lab Library Foreign Students Cell Corporate Training Hardware Lab Placement Cell Hostel Facility Classrooms Placement Companies     Contact Details Vector Institute # 502, Nagasuri Plaza (Bank Of India building) Behind Maithrivanam, Ameerpet, Hyderabad - 500038 Email : info@vectorindia.org Map Image

__________________ Answered By StudyChaCha Member |