|

#1

| |||

| |||

|

I am looking for JNTUK CSE Old papers, form which sources I can obtain this?

|

|

#2

| |||

| |||

|

As per your need here I am providing JNTUK CSE Old papers; 1. a) Determine the single error correcting code for the message code: 10110 for an odd parity system. b) How many 1’s are present in the unsigned binary representation of the value of the decimal expressions: 32768 X 4 + 1024 X 8 + 32 X 16 + 32? c) If (1.001)1259 = 3.52 and (1.001)2062 = 7.85, then what is the value of: (1.001)3321? (6M+5M+5M) 2. a) A computer has 48 bit instructions and 12 bit addresses. If there are ‘S’ three address instructions, ‘D’ two address instructions and ‘V’ address instructions, then how many zero address instructions can be formulated? b) Write a program for the relatively simple CPU that can evaluate the arithmetic expression X = (A + B) * (C + D) by a three address, two address, one address and zero address instructions. Assume that the processor has the instructions: LOAD, STORE, MUL, ADD, MOV, PUSH, POP (8M+8M) 3. a) What is a microinstruction? Compare horizontal and vertical microinstructions. b) What are the two methods to reduce the number of microinstructions needed by the control unit? Explain, in detail, with suitable examples. (8M+8M) 4. a) Explain the Booth’s algorithm for signed number multiplication. b) What is the Booth’s coding in 10 bits for the decimal number: -100? c) A digital computer uses a floating point representation comprising a signed magnitude fractional mantissa and an excess-16, radix-4 exponent. What decimal number is represented by a floating point number whose exponent is 10101 and mantissa is 111000 and the sign bit set? (5M+5M+6M) 5. a) What is a page? When do page faults occur? The address sequence generated by tracing a particular program executing in a pure demand paging system, with 100 records per page and one free main memory frame is recorded as follows: 0100, 0210, 0430, 0499, 0510, 0530, 0560, 0120, 0220, 0240, 0260, 0320, 0370, and 0360. What is the total number of pages which will not occur page faults? b) What is a segment? What is a paged segmentation? Consider the following segment table with segment number, segment length and segment base address: For collect more paper you have to download this attached file: JNTUK CSE Old papers myheartdreams.in/EXAMSADDA/QUESTION%20PAPERS/2012/R07/2-2%20SUPPLY%20EXAMS%20%20April%20–%202012%20(www.examsadda.com)/CSE%20(www.examsadda.com).zip

__________________ https://t.me/pump_upp |

|

#4

| |||

| |||

|

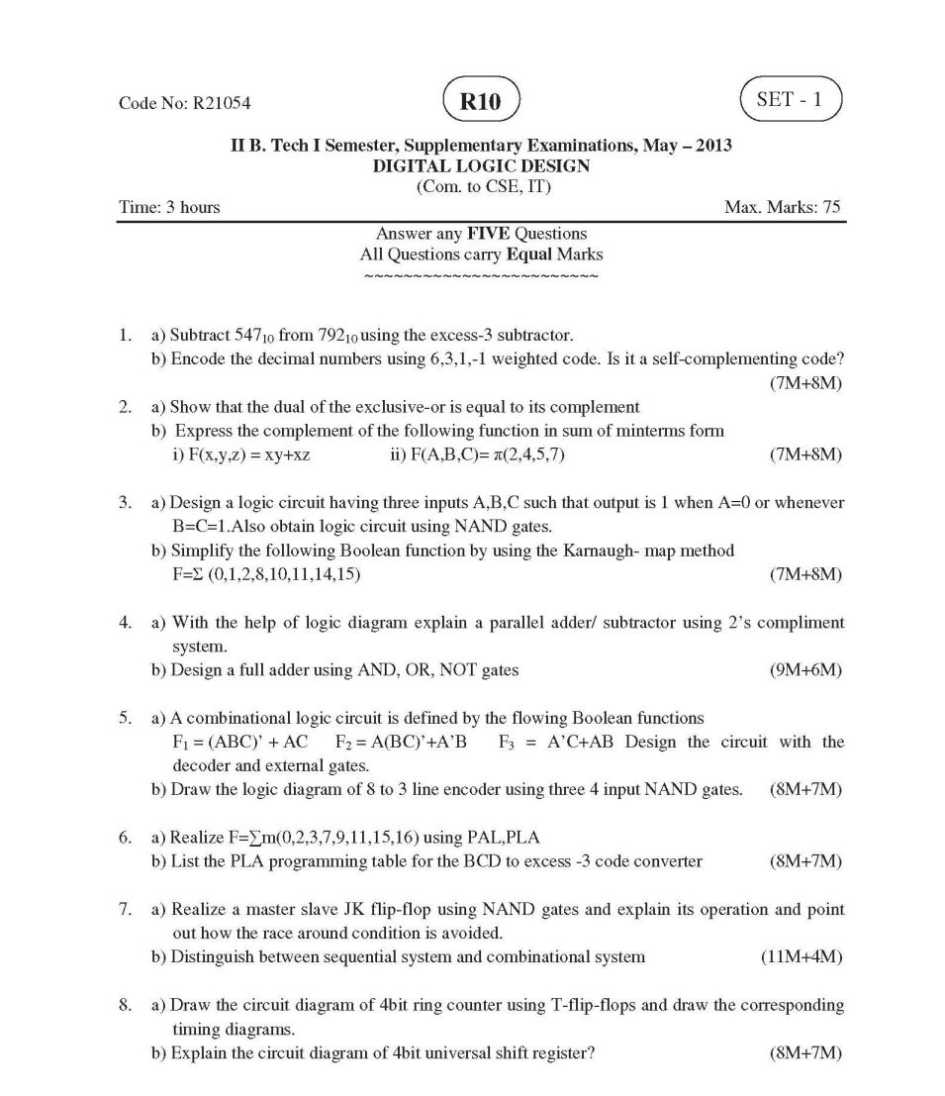

Here is the list of few questions of JNTU B.TECH CSE Digital Logic Design exam question paper which you are looking for . 1. a) Subtract 54710 from 79210 using the excess-3 subtractor. b) Encode the decimal numbers using 6,3,1,-1 weighted code. Is it a self-complementing code? (7M+8M) 2. a) Show that the dual of the exclusive-or is equal to its complement b) Express the complement of the following function in sum of minterms form i) F(x,y,z) = xy+xz ii) F(A,B,C)= _(2,4,5,7) (7M+8M) 3. a) Design a logic circuit having three inputs A,B,C such that output is 1 when A=0 or whenever B=C=1.Also obtain logic circuit using NAND gates. b) Simplify the following Boolean function by using the Karnaugh- map method F=_ (0,1,2,8,10,11,14,15) (7M+8M) 4. a) With the help of logic diagram explain a parallel adder/ subtractor using 2’s compliment system. b) Design a full adder using AND, OR, NOT gates (9M+6M) 5. a) A combinational logic circuit is defined by the flowing Boolean functions F1 = (ABC)’ + AC F2 = A(BC)’+A’B F3 = A’C+AB Design the circuit with the decoder and external gates. b) Draw the logic diagram of 8 to 3 line encoder using three 4 input NAND gates. (8M+7M) 6. a) Realize F=_m(0,2,3,7,9,11,15,16) using PAL,PLA b) List the PLA programming table for the BCD to excess -3 code converter (8M+7M) 7. a) Realize a master slave JK flip-flop using NAND gates and explain its operation and point out how the race around condition is avoided. b) Distinguish between sequential system and combinational system

__________________ Answered By StudyChaCha Member |